-

Notifications

You must be signed in to change notification settings - Fork 586

Projects

Collections of projects with LiteX involved that could be useful for users to better understand LiteX, go further and/or find some inspiration.

__ _

/ / (_)__ __ ____ __

/ /__/ / _ \/ // /\ \ /

/____/_/_//_/\_,_//_\_\

/ _ \/ _ \

__ _ __ _\___/_//_/ __ _

/ / (_) /____ | |/_/__| | / /____ __ ____(_)__ _____ __

/ /__/ / __/ -_)> </___/ |/ / -_) \ // __/ (_-</ __/ |/ /

/____/_/\__/\__/_/|_| |___/\__/_\_\/_/ /_/___/\__/|___/

Copyright (c) 2019-2020, Linux on LiteX VexRiscv Developers

- Have an FPGA board with 32MB of RAM and want to test Linux on it?

- Want to study/explore a RISC-V Linux capable SoC?

- Want to create a full autonomous SoC with LiteX and its peripherals (SPI, I2C, SDCard, FrameBuffer, etc...) managed by Linux?

Linux-on-LiteX-VexRiscv project demonstrates how to create a Linux capable SoC with VexRiscv CPU, a 32-bits Linux Capable RISC-V CPU written in Spinal HDL. A SoC around the VexRiscv CPU is created using LiteX as the SoC builder and LiteX's cores written in Migen Python DSL (LiteDRAM, LiteEth, LiteSDCard). All the components used to create the SoC are open-source and the flexibility of Spinal HDL/Migen allow targeting easily very various FPGA devices/boards: Lattice, Altera, Xilinx, Microsemi FPGAs with SDRAM/DDR/DDR2/DDR3/DDR4 RAMs, RMII/MII/RGMII/1000BASE-X Ethernet PHYs. On Lattice ECP5 FPGAs, the open source toolchain allows creating full open-source SoC with open-source cores and toolchain!

This project demonstrates how high level HDLs (Spinal HDL, Migen) enable new possibilities and complement each other. Results shown there are the results of a productive collaboration between open-source communities.ant to test easily control LiteX cores.

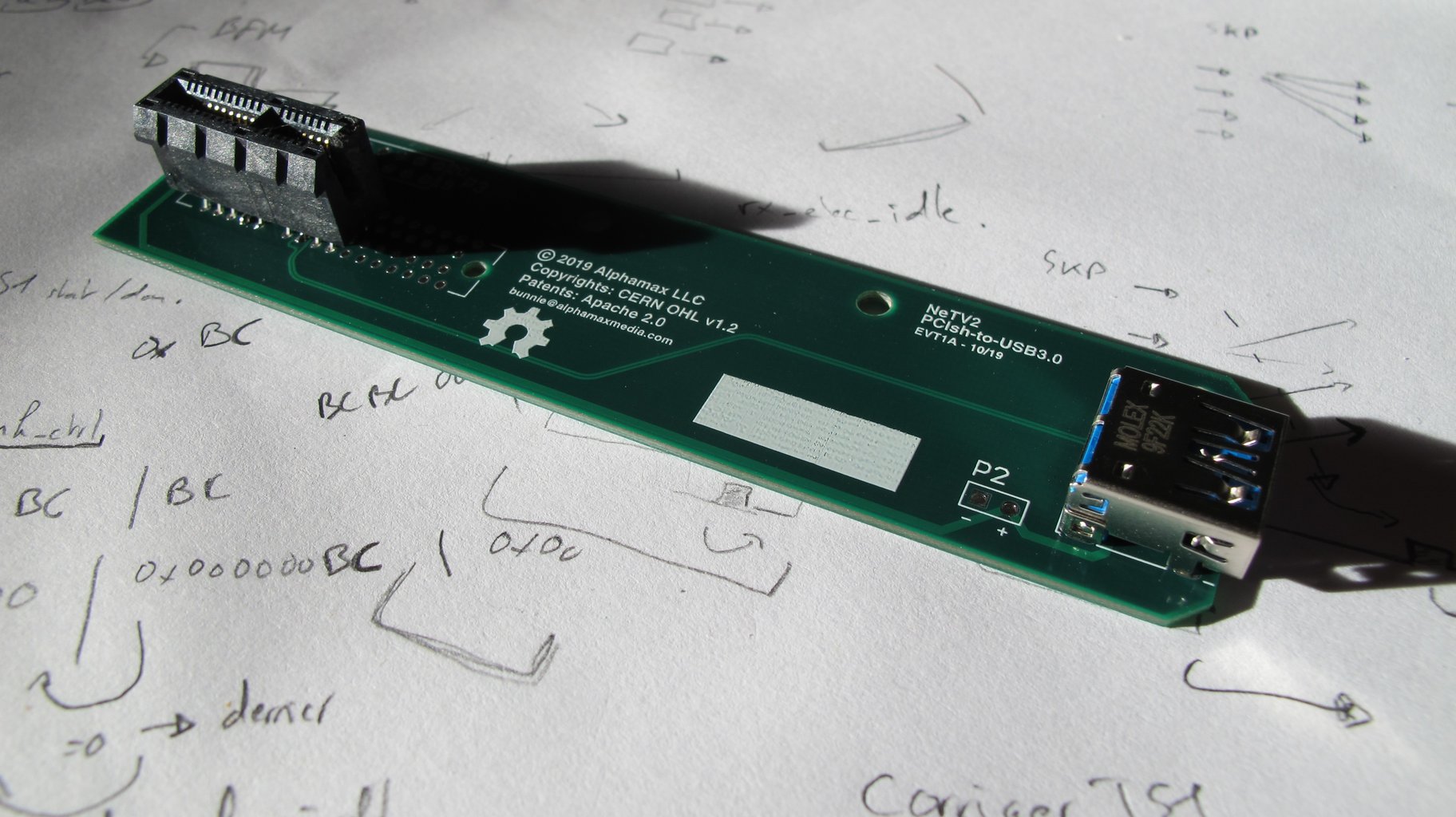

FIXME: add description

FIXME: add description

FIXME: add description

FIXME: add description

FIXME: add description

FIXME: add description

FIXME: add description

FIXME: add description

Have a question or want to get in touch? Our IRC channel is #litex at irc.libera.chat.

- Welcome to LiteX

- LiteX's internals

- How to

- Create a minimal SoC-TODO

- Add a new Board-TODO

- Add a new Core-WIP

- Add a new CPU-WIP

- Reuse-a-(System)Verilog,-VHDL,-Amaranth,-Spinal-HDL,-Chisel-core

- Use LiteX on the Acorn CLE 215+

- Load application code the CPU(s)

- Use Host Bridges to control/debug a SoC

- Use LiteScope to debug a SoC

- JTAG/GDB Debugging with VexRiscv CPU

- JTAG/GDB Debugging with VexRiscv-SMP, NaxRiscv and VexiiRiscv CPUs

- Document a SoC

- How to (Advanced)